AMD Gives Details on EPYC Zen4: Genoa and Bergamo, up to 96 and 128 Cores

by Dr. Ian Cutress on November 8, 2021 11:39 AM EST

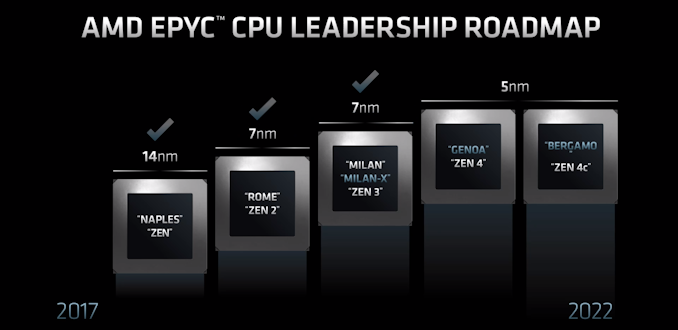

Since AMD’s relaunch into high-performance x86 processor design, one of the fundamental targets for the company was to be a competitive force in the data center. By having a competitive product that customers could trust, the goal has always been to target what the customer wants, and subsequently grow market share and revenue. Since the launch of 3rd Generation EPYC, AMD is growing its enterprise revenue at a good pace, however questions always turn around to what the roadmap might hold. In the past, AMD has disclosed that its 4th Generation EPYC, known as Genoa, would be coming in 2022 with Zen 4 cores built on TSMC 5nm. Today, AMD is expanding the Zen 4 family with another segment of cloud-optimized processors called Bergamo.

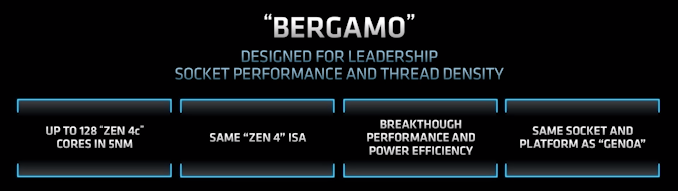

As part of AMD’s Data Center event today, the company is showcasing that its 4th Generation EPYC roadmap will consist of two segments: Genoa, with up to 96 Zen 4 cores, and Bergamo, with up to 128 Zen 4c cores. Not only are we getting official confirmation of core counts, but AMD is disclosing that Bergamo will be using a different type of core: the Zen 4c core.

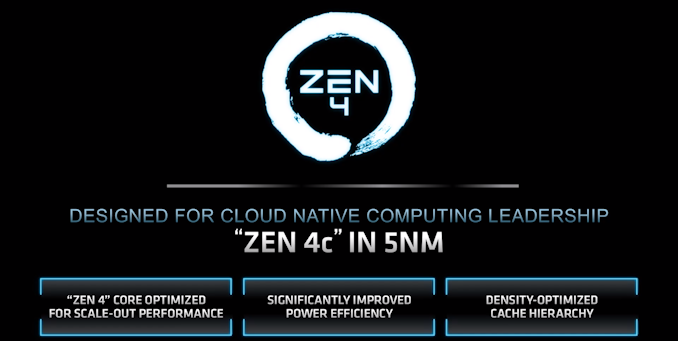

The ‘c’ in this instance means ‘cloud optimized’. AMD has built two different forms of Zen 4 core, one for most applications, and a higher density version for the cloud. This means that these two cores, while functionally identical, will use different sets of masks. The Zen 4c core has been redesigned to have the same functionality but offer more density combined with a different power/performance point on the voltage frequency curve. This is going to affect power consumption, efficiency, and likely the range of frequencies available. AMD confirmed that Bergamo is likely to see the power window of enterprise CPUs expand too: normally we see server CPUs in the 65-280W range, but Zen4/4c will go further (in both directions) to cater for specific cloud use cases that might rely on density, performance, or efficiency. The Zen4c core is likely to be smaller in order to fit 128 cores, and have different amounts of cache to Zen4, so there could be an IPC difference to the traditional Zen4 core.

AMD has stated to us in our briefing that Genoa and Bergamo will be socket compatible, with Genoa coming in the 2022 timeframe, while Bergamo in late 2022/early 2023 (with a focus more on the early 2023 target). When asked, AMD did not want to narrow down the Genoa timeframe in a similar light. Bergamo however will have the same features as Genoa: DDR5, PCIe 5.0, CXL 1.1, RAS, and AMD's security suite.

The use of two different core optimization points is going to be an interesting one for AMD. Normally it creates one core chiplet design that can be used across consumer and server processors, but the development of a Zen 4c chiplet now means the company has to manage stock of both independently. Also, both being on 5nm means that the mask development costs are likely to be double than a singular design across all. AMD did not disclose any new details about a centralized IO die – what is on it, or where it was made.

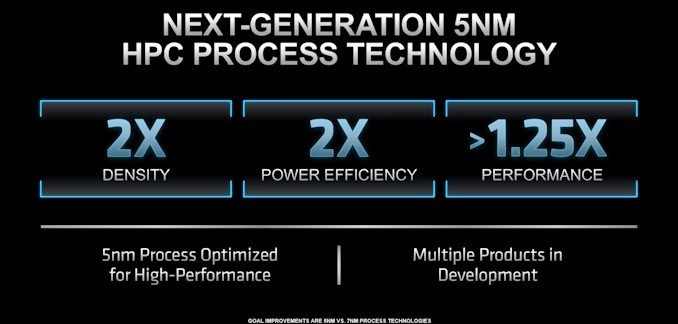

The Zen 4c chiplet, according to AMD, is built on an HPC variant of TSMC N5. This aims at denser logic and denser cache, likely at the expense of high-end frequency. AMD says that this process offers 2x density, 2x power efficiency, and >1.25x silicon performance over the regular N7 it uses. When asked if this was a specific statement about core performance, AMD said that it wasn’t, and just a comment on the process node technologies. It is worth noting that 2x efficiency is quite a substantial claim based on metrics provided by TSMC on its N7 -> N5 disclosures.

With Bergamo targeted specifically for the cloud, and cloud instances, I wonder if we will ever get to test it in a local system akin to a regular review. One of AMD’s features in previous generation EPYCs is processor locking, which limits a CPU to a particular vendor’s motherboards. We’ve seen this with some of Lenovo’s systems, for example. This feature allows for supply chain control, which is requested by certain customers.

We are told that more information is to follow in the coming months.

35 Comments

View All Comments

flyingpants265 - Monday, November 8, 2021 - link

How much of this stuff really matters?nandnandnand - Monday, November 8, 2021 - link

AMD can use a new chiplet like Zen 4c to do their own take on big.LITTLE.The 3D V-Cache is nice too, even better for Epyc than Ryzen.

TomWomack - Monday, November 8, 2021 - link

Indeed: I suspect Zen 4c will be facing off against systems built with Gracemont cores and Sapphire Rapids' multi-die technology to get more than 200 x86 cores in a socket. I don't know how many memory controllers Intel will be wielding at that point - pin counts and motherboard traces are already getting inconvenient at 8-way DDR5.Silver5urfer - Monday, November 8, 2021 - link

Gracemont is garbage vs Zen 4C. The former is SKL Idk all you guys do not read AT or what ? go to 12900K review check out the E core performance where they clearly mention how it is it's competing against a 6700K CPU.Zen 4C is sharing socket with damn Zen 4 which Lisa Su flat out mentioned in the press brief that it will be world's fastest GPC, General Purpose Compute CPU. That already defines Sapphire Rapids is going to get rekt.

The only reason they are doing it is ARM processors, usually ARM CPUs have high thread density without Hyperthreading a.k.a no SMT2 so AMD is going on them with Zen 4c Bergamo with massive 128 Core design.

There's no Multi Die Technology going on at Intel, Sapphire Rapids is 14C/Tile with 4 Tiles totaling to 56Core design on a single PCB with EMIB Foveros with same Golden Cove P cores that power Alder Lake but with lower Clocks ofc.

Also AMD clearly last time mentioned they are not interested in Big.little formula recently that too. I don't think AMD is going to copy Intel's weak Client strategy. Intel 7 a.k.a Intel 10nmESF is either 3rd or 4th iteration of 10nm - Lakefield (10nm), Tigerlake (10nmSF) and it cannot contain Golden Cove P cores at 5GHz also if you see the power consumption and heat of the ADL 12900K CPU you will see how 200W of ADL = 90C, vs 200W of CML = 75C. That's super dense so they cannot package them more than 8C at 5GHz which is why Intel got the new big little bs formula and they do not need them because they can get away with P core performance.

Ultimately my guess is AMD Is going for 2 SKU approach rather than bumbling the core formula, I really wish infact they do that. Like give the AM5 a full fat beefy Zen 4 CPU 16C32T called 7950X and the Zen 4c based 7850C at 32T but it doesn't serve any purpose, maybe they will create 7550H which has 24T of Zen 4c to combat ADL.

mode_13h - Monday, November 8, 2021 - link

What is Zen 3+ and when is it expected?nandnandnand - Monday, November 8, 2021 - link

Zen 3+ has been used to refer to an allegedly cancelled refresh of Zen 3 Vermeer, called "Warhol", as well as the cores in Rembrandt APUs, which should be announced in January.Take Parham's list with a lot of salt.

nandnandnand - Monday, November 8, 2021 - link

AMD was claiming some massive performance increases for Milan-X, but I didn't hear them give an average % increase. 768 MB of cache is clearly a different ballgame from 192 MB though.lightningz71 - Monday, November 8, 2021 - link

It's also substantially lower latency than HBM cache based designs...Rudde - Monday, November 8, 2021 - link

2x density and 2x efficiency should allow AMD to make 16 core CCDs with an area below 80mm² at the same power consumption as the current 8 core CCDs. A 128 core CPU would look similar to the current 64 core CPUs.Wrs - Monday, November 8, 2021 - link

Yes but the performance per core would suffer a lot. 1.25x performance per area. But I think they were only referring to Bergamo which is tailored for cheap cloud instances.