Intel Showcases Sapphire Rapids Plus HBM Xeon Performance at ISC 2022

by Ryan Smith on May 31, 2022 12:30 PM EST

Alongside today’s disclosure of the Rialto Bridge accelerator, Intel is also using this week’s ISC event to deliver a brief update on Sapphire Rapids, the company’s next-generation Xeon CPU which is shipping later this year. While Intel has been beating the drum for their forthcoming, 4th Generation Xeon Scalable chip for a while, we have yet to hear anything of significance about its expected performance – particularly in the HPC space. So ahead of its formal launch a bit later this year, Intel is finally talking a bit about the expected performance of the HBM-equipped version of the chip, which is aimed in particular at the HPC/supercomputing crowd.

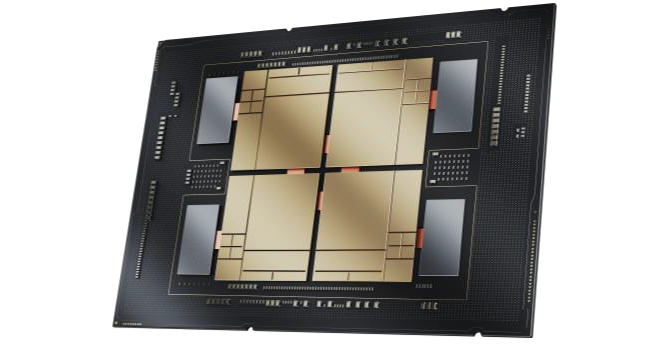

Intel’s first tiled Xeon processor, Sapphire Rapids is also Intel’s first CPU to offer optional on-chip HBM memory, which is being dubbed Sapphire Rapids Plus HBM. The addition of 64GB of HBM2e makes it a fairly complex and expensive chip, but also one with access to far more memory bandwidth than any x86 CPU before it. As a result, the chip is of particular interest to a subset of the high-performance compute community, as it offers an alternative route for workloads that aren’t suitable for GPUs, but still need access to vast amounts of memory bandwidth.

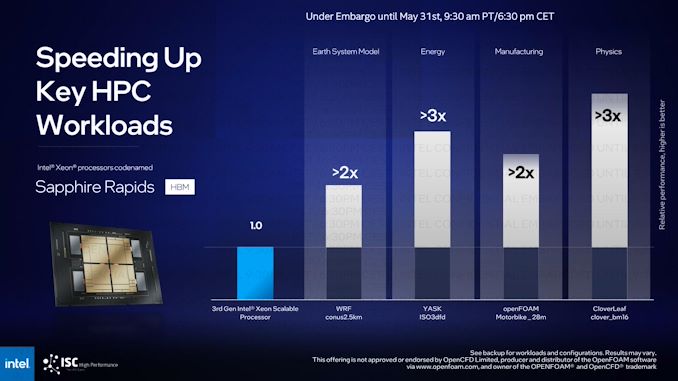

As part of their ISC presentation today, Intel is releasing two slides with performance figures for the HBM version of Sapphire Rapids (Sapphire Rapids Plus HBM). The idea here is to show off the combination of architecture improvements – and in particular, the dedicated accelerator blocks – combined with using 64GB of HBM2e memory to keep those blocks well fed. The pre-production processors are being compared to Intel’s Xeon Platinum 8380 (Ice Lake-SP) chips.

Bearing in mind that these are going to be cherry-picked performance figures, Intel is seeing anywhere between a 2x speed-up in things like the WRF weather forecasting model, to over a 3x improvement for the CloverLeaf Euler equation solver. Both of which are somewhat narrow use cases, but important ones for the HPC market segment.

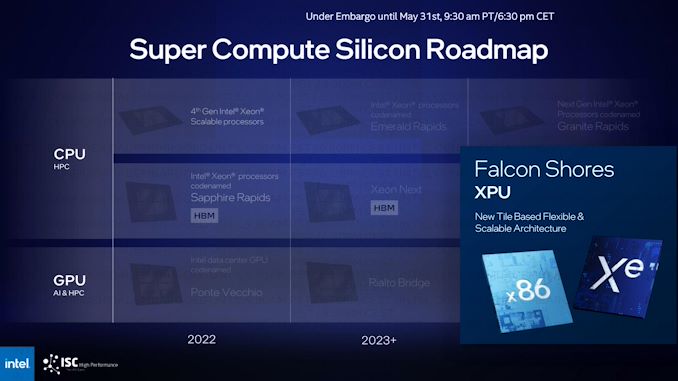

Sapphire Rapids Plus HBM is due to be released alongside the rest of the Sapphire Rapids family later this year. According to Intel’s current roadmaps, it is due for a successor in the 2023 timeframe, before the entire HBM-equipped Xeon lineup is due to be rolled into the Falcon Shores XPU in 2024.

21 Comments

View All Comments

lemurbutton - Wednesday, June 1, 2022 - link

x86 is not that interesting anymore. Anandtech needs to cover ARM server chips and ARM laptop/desktop chips more.nandnandnand - Wednesday, June 1, 2022 - link

ARM is cringe. x86 will be with us for another 20 years.lemurbutton - Wednesday, June 1, 2022 - link

Yes. PowerPC chips are still here. Doesn't mean that it's relevant.x86 is out. Get with the times.

BushLin - Wednesday, June 1, 2022 - link

LOL, get with the software market, flexible platform, support and boot options. Who wants to back to the bad old days of total vendor lockdown either?Otritus - Wednesday, June 1, 2022 - link

Can you please point out the retail devices with ARM laptop or desktop chips that deliver good performance and efficiency without an Apple logo? Maybe the DIY desktop ARM chips that deliver better performance per watt than Zen 3 and better performance per dollar than Alder Lake? ARM server is pretty interesting, but x86 is still competitive.The primary reason why x86 chips are bad is because AMD and Intel are fighting the GHz wars. Doubling clock speeds require a quadrupling in transistors, if there is a hardware frequency limit, or more than an octupling in power if there isn’t a hardware frequency limit. With ARM chips running at 3/5 the frequency of x86, it only makes sense that they are smaller and significantly more power efficient. People like to point out that the x86 ISA is bloated with legacy instruction sets, but the bloat is less than 5% on modern processors. If we take into account that x86 processes instructions poorly relative to ARM, you may hit a 10% efficiency, which while measurable, isn’t that significant. Also, if you care about ISA problems, then RISC-V should be used.

usiname - Monday, June 6, 2022 - link

You have not idea how the thigs work. Increasing of the frequency does not require increase in the transistor count. Exactly the opposite, you runing same transistor at higher frequency. M1 ultra has 114b transistors, and is slower than single 5950x(19b) + rtx 3090ti(28.3). Imagine to be slower while waste so much transistors. This is bexause the lower clock speedsDante Verizon - Wednesday, June 1, 2022 - link

Go Home, you are drunk. The world is x86. period.Qasar - Wednesday, June 1, 2022 - link

lemurbutton isnt drunk, hes just an apple fanboy who posts pretty much the same praise for apple every time and thinks m1 is the best and only cpu out thereBushLin - Wednesday, June 1, 2022 - link

x86 is about as exciting as it has ever been if you look at the next two years of upcoming products. Until a common boot method and wide driver support exists for ARM it is the preserve of fixed products with limited choice... Like the 70s and early 80s but now we have better options, like the well established x86 market.Gondalf - Wednesday, June 1, 2022 - link

This wrong, many Pro Tech sites dedicated to enterprise or other segments of server market, realized that in average actual Xeon is exactly on pair with Milan, doing a serious comparison with real world SW and real world workloads. So you are absolurely wrong. In fact actual Xeon is selling at record level, Milan nope.