Update: PCI Express 6.0 Draft 0.71 Released, Final Release by End of Year

by Ryan Smith on July 2, 2021 7:00 AM EST- Posted in

- CPUs

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

Update 07/02: Albeit a couple of days later than expected, the PCI-SIG has announced this morning that the PCI Express draft 0.71 specification has been released for member review. Following a minimum 30 day review process, the group will be able to publish the draft 0.9 version of the specficiation, putting them on schedule to release the final version of the spec this year.

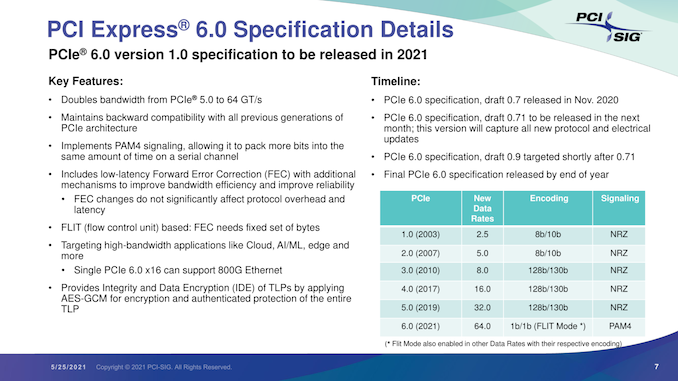

Originally Published 05/25

As part of their yearly developer conference, the PCI Special Interest Group (PCI-SIG) also held their annual press briefing today, offering an update on the state of the organization and its standards. The star of the show, of course, was PCI Express 6.0, the upcoming update to the bus standard that will once again double its data transfer rate. PCI-SIG has been working on PCIe 6.0 for a couple of years now, and in a brief update, confirmed that the group remains on track to release the final version of the specification by the end of this year.

The most recent draft version of the specification, 0.7, was released back in November. Since then, PCI-SIG has remained at work collecting feedback from its members, and is gearing up to release another draft update next month. That draft will incorporate the all of the new protocol and electrical updates that have been approved for the spec since 0.7.

In a bit of a departure from the usual workflow for the group, however, this upcoming draft will be 0.71, meaning that PCIe 6.0 will be remaining at draft 0.7x status for a little while longer. The substance of this decision being that the group is essentially going to hold for another round of review and testing before finally clearing the spec to move on to the next major draft. Overall, the group’s rules call for a 30-day review period for the 0.71 draft, after which the group will be able to release the final draft 0.9 specification.

Ultimately, all of this is to say that PCIe 6.0 remains on track for its previously-scheduled 2021 release. After draft 0.9 lands, there will be a further two-month review for any final issues (primarily legal), and, assuming the standard clears that check, PCI-SIG will be able to issue the final, 1.0 version of the PCIe 6.0 specification.

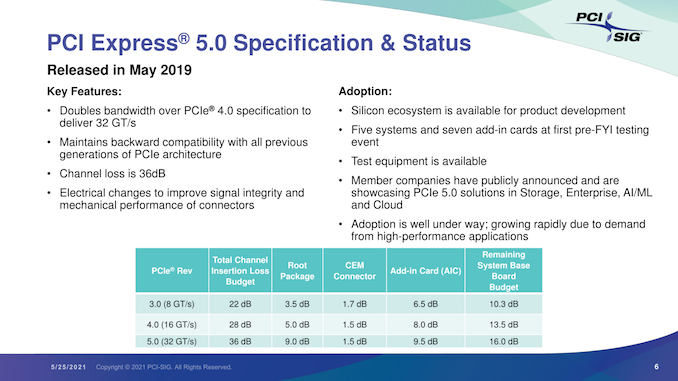

In the interim, the 0.9 specification is likely to be the most interesting from a technical perspective. Once the updated electrical and protocol specs are approved, the group will be able to give some clearer guidance on the signal integrity requirements for PCIe 6.0. All told we’re not expecting much different from 5.0 (in other words, only a slot or two on most consumer motherboards), but as each successive generation ratchets up the signaling rate, the signal integrity requirements have tightened.

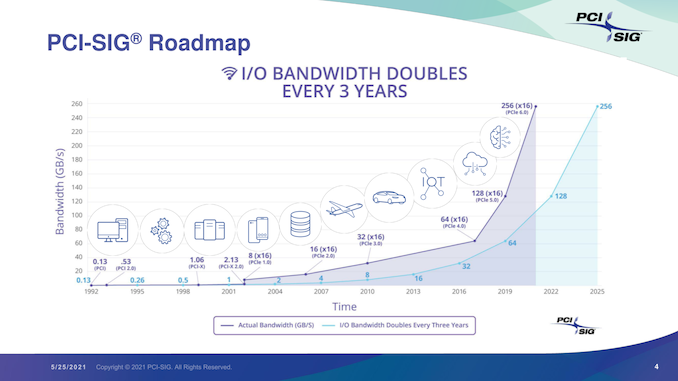

Overall, the unabashedly nerdy standards group is excited about the 6.0 standard, comparing it in significance to the big jump from PCIe 2.0 to PCIe 3.0. Besides proving that they’re once again able to double the bandwidth of the ubiquitous bus, it will mean that they’ve been able to keep to their goal of a three-year cadence. Meanwhile, as the PCIe 6.0 specification reaches completion, we should finally begin seeing the first PCIe 5.0 devices show up in the enterprise market.

103 Comments

View All Comments

Ryan Smith - Tuesday, May 25, 2021 - link

Thanks!damianrobertjones - Wednesday, May 26, 2021 - link

Double every three years? Why? To max profits? Just go for the fastest you can achieve at the time. Stop milking people year after year.willis936 - Wednesday, May 26, 2021 - link

Because the market demands it. Technology actually improving isn't milking. That would be Intel selling 4 cores for the same price for 10 years.melgross - Wednesday, May 26, 2021 - link

It’s technology. It always improves. Giving a three year schedule is helpful for manufactures. Like it or not, that’s important.mode_13h - Wednesday, May 26, 2021 - link

> Double every three years? Why? To max profits?This ain't about you, dude. This is about hyperscalers who want 800 Gigabit Ethernet and about datacenter GPUs that want to stream vast amounts of data in/out of system RAM.

Santoval - Wednesday, May 26, 2021 - link

Does PCIe 6.0's 1b/1b encoding mean zero encoding overhead? Is this really possible? It's also unclear if "FLIT mode" is always active or not, and what exactly does this mean (I looked it up and FLIT is apparently the acronym for "Flow Control Unit").Elsewhere I read that that PCIe 6.0, due to the switch to PAM4 signaling, has a staggering 3 orders of magnitude (i.e. 1000 times) higher bit-error rate than PCIe 5.0, thus the need for FEC. While this sounds unreasonably high the error rate of PCIe up to version 5.0 is reportedly extremely low to begin with, so FEC can handle the error rate of PCIe 6.0 with minimal extra latency (the target is an astoundingly low 1 - 2 ns of extra latency due to FEC, while the FEC variant used on Ethernet adds ~100 ns of latency)

willis936 - Wednesday, May 26, 2021 - link

PAM4 certainly kills SNR. EQ tuning becomes massively important. It looks like they specify tuning of DFE and CTLE to minimize BER, but I suppose that only buys so much.Idk what you consider "astonishingly low" for effective BER, but anything above 10^-18 is too high for an interconnect this fast and with this application is way too high imo. I don't see the numbers mentioned in the article.

Line coding's signal integrity benefits are made obsolete by FEC. I don't full understand FLIT, but it appears to be their "lightweight" FEC implementation that allows for low latency. IEEE 802.3 know their business. A lot of this PAM4 is copy and paste from bs. I'm wary of places where they deviate, such as saying "100 ns is too long, we'll just make the FEC worse and retransmit more". That sends of red flags to me. Your effective throughput will greatly suffer if you rely on retransmission. Thou shalt not violate Shannon's limit.

mode_13h - Wednesday, May 26, 2021 - link

> the FEC variant used on Ethernet adds ~100 ns of latencyAt what speed of Ethernet? At 1 Gbps, a bit takes 1 ns. The CRC of an Ethernet frame is 32-bits. So, if that's what you're talking about, it should add 32 ns, at Gigabit speeds.

Really, rather than get carried away with ns, just look at the relative data sizes of FEC and the frame or packet size. The controller has to process it at wire-speed, and is almost certainly doing so as it reads bits (or PAM4 symbols) off the wire.

EthiaW - Wednesday, May 26, 2021 - link

So where is the ceiling of copper sockets?CiccioB - Thursday, May 27, 2021 - link

It depends on how far you want to go with the signals, which max latency you are targeting and most of all, how much energy you want to spend for each bit.There's not a theoretical maximum speed you can achieve.