Apple's M1 Pro, M1 Max SoCs Investigated: New Performance and Efficiency Heights

by Andrei Frumusanu on October 25, 2021 9:00 AM EST- Posted in

- Laptops

- Apple

- MacBook

- Apple M1 Pro

- Apple M1 Max

Huge Memory Bandwidth, but not for every Block

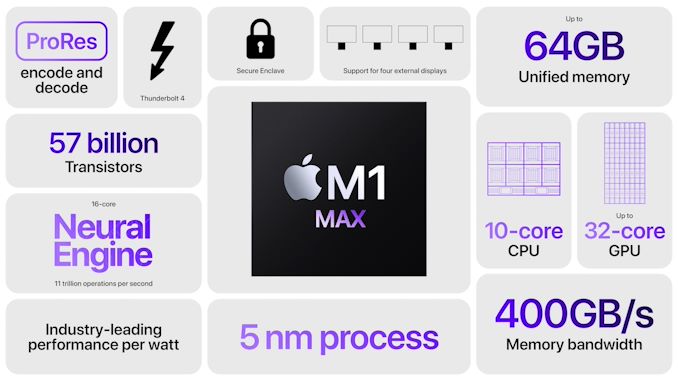

One highly intriguing aspect of the M1 Max, maybe less so for the M1 Pro, is the massive memory bandwidth that is available for the SoC.

Apple was keen to market their 400GB/s figure during the launch, but this number is so wild and out there that there’s just a lot of questions left open as to how the chip is able to take advantage of this kind of bandwidth, so it’s one of the first things to investigate.

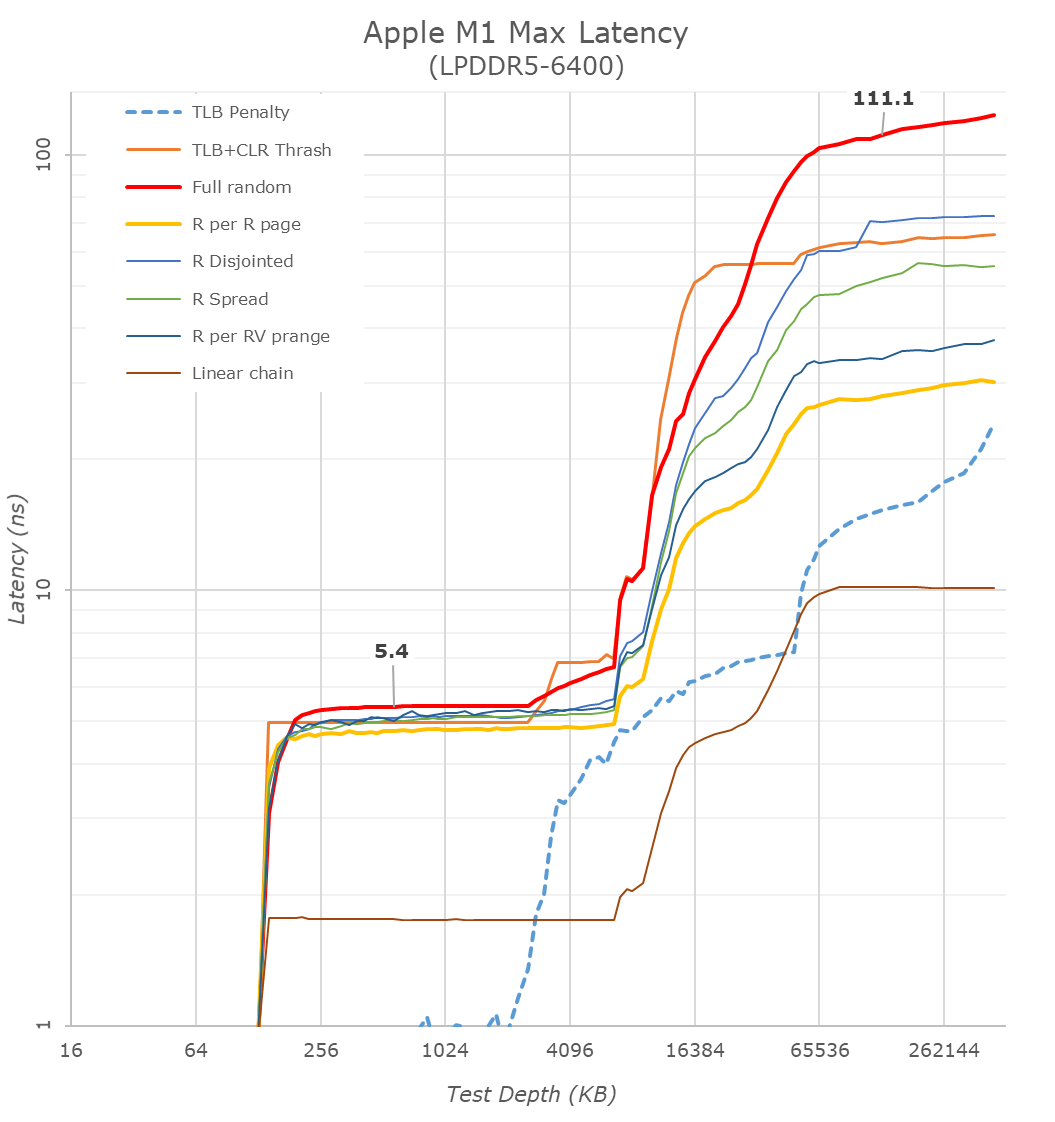

Starting off with our memory latency tests, the new M1 Max changes system memory behaviour quite significantly compared to what we’ve seen on the M1. On the core and L2 side of things, there haven’t been any changes and we consequently don’t see much alterations in terms of the results – it’s still a 3.2GHz peak core with 128KB of L1D at 3 cycles load-load latencies, and a 12MB L2 cache.

Where things are quite different is when we enter the system cache, instead of 8MB, on the M1 Max it’s now 48MB large, and also a lot more noticeable in the latency graph. While being much larger, it’s also evidently slower than the M1 SLC – the exact figures here depend on access pattern, but even the linear chain access shows that data has to travel a longer distance than the M1 and corresponding A-chips.

DRAM latency, even though on paper is faster for the M1 Max in terms of frequency on bandwidth, goes up this generation. At a 128MB comparable test depth, the new chip is roughly 15ns slower. The larger SLCs, more complex chip fabric, as well as possible worse timings on the part of the new LPDDR5 memory all could add to the regression we’re seeing here. In practical terms, because the SLC is so much bigger this generation, workloads latencies should still be lower for the M1 Max due to the higher cache hit rates, so performance shouldn’t regress.

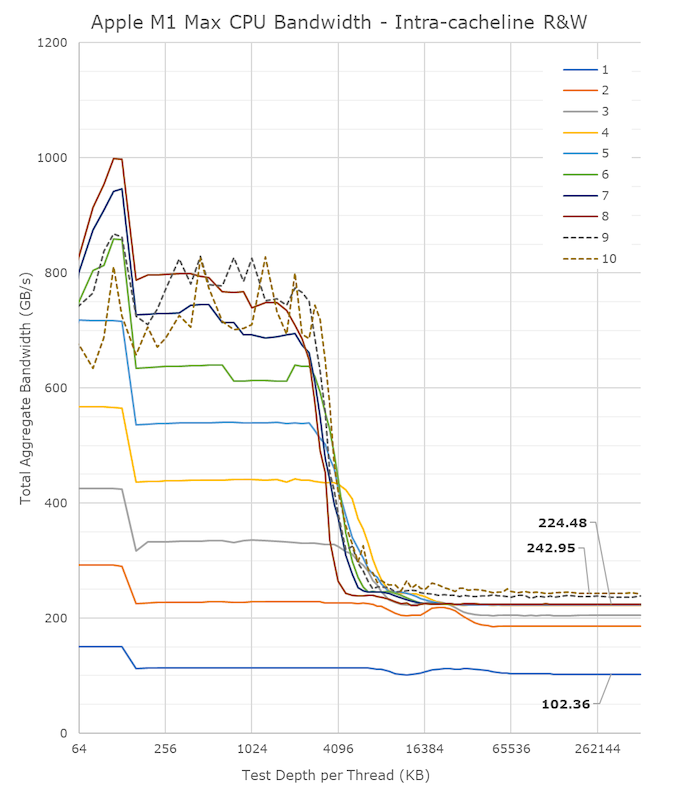

A lot of people in the HPC audience were extremely intrigued to see a chip with such massive bandwidth – not because they care about GPU or other offload engines of the SoC, but because the possibility of the CPUs being able to have access to such immense bandwidth, something that otherwise is only possible to achieve on larger server-class CPUs that cost a multitude of what the new MacBook Pros are sold at. It was also one of the first things I tested out – to see exactly just how much bandwidth the CPU cores have access to.

Unfortunately, the news here isn’t the best case-scenario that we hoped for, as the M1 Max isn’t able to fully saturate the SoC bandwidth from just the CPU side;

From a single core perspective, meaning from a single software thread, things are quite impressive for the chip, as it’s able to stress the memory fabric to up to 102GB/s. This is extremely impressive and outperforms any other design in the industry by multiple factors, we had already noted that the M1 chip was able to fully saturate its memory bandwidth with a single core and that the bottleneck had been on the DRAM itself. On the M1 Max, it seems that we’re hitting the limit of what a core can do – or more precisely, a limit to what the CPU cluster can do.

The little hump between 12MB and 64MB should be the SLC of 48MB in size, the reduction in BW at the 12MB figure signals that the core is somehow limited in bandwidth when evicting cache lines back to the upper memory system. Our test here consists of reading, modifying, and writing back cache lines, with a 1:1 R/W ratio.

Going from 1 core/threads to 2, what the system is actually doing is spreading the workload across the two performance clusters of the SoC, so both threads are on their own cluster and have full access to the 12MB of L2. The “hump” after 12MB reduces in size, ending earlier now at +24MB, which makes sense as the 48MB SLC is now shared amongst two cores. Bandwidth here increases to 186GB/s.

Adding a third thread there’s a bit of an imbalance across the clusters, DRAM bandwidth goes to 204GB/s, but a fourth thread lands us at 224GB/s and this appears to be the limit on the SoC fabric that the CPUs are able to achieve, as adding additional cores and threads beyond this point does not increase the bandwidth to DRAM at all. It’s only when the E-cores, which are in their own cluster, are added in, when the bandwidth is able to jump up again, to a maximum of 243GB/s.

While 243GB/s is massive, and overshadows any other design in the industry, it’s still quite far from the 409GB/s the chip is capable of. More importantly for the M1 Max, it’s only slightly higher than the 204GB/s limit of the M1 Pro, so from a CPU-only workload perspective, it doesn’t appear to make sense to get the Max if one is focused just on CPU bandwidth.

That begs the question, why does the M1 Max have such massive bandwidth? The GPU naturally comes to mind, however in my testing, I’ve had extreme trouble to find workloads that would stress the GPU sufficiently to take advantage of the available bandwidth. Granted, this is also an issue of lacking workloads, but for actual 3D rendering and benchmarks, I haven’t seen the GPU use more than 90GB/s (measured via system performance counters). While I’m sure there’s some productivity workload out there where the GPU is able to stretch its legs, we haven’t been able to identify them yet.

That leaves everything else which is on the SoC, media engine, NPU, and just workloads that would simply stress all parts of the chip at the same time. The new media engine on the M1 Pro and Max are now able to decode and encode ProRes RAW formats, the above clip is a 5K 12bit sample with a bitrate of 1.59Gbps, and the M1 Max is not only able to play it back in real-time, it’s able to do it at multiple times the speed, with seamless immediate seeking. Doing the same thing on my 5900X machine results in single-digit frames. The SoC DRAM bandwidth while seeking around was at around 40-50GB/s – I imagine that workloads that stress CPU, GPU, media engines all at the same time would be able to take advantage of the full system memory bandwidth, and allow the M1 Max to stretch its legs and differentiate itself more from the M1 Pro and other systems.

493 Comments

View All Comments

id4andrei - Monday, October 25, 2021 - link

Hey Andrei, on gaming, how does the API difference weigh in? I assume that Apple expects all devs to design their new games with Metal in mind. On the Windows side you have DX, OpenGL, Vulkan and the GPUs themselves are tuned to various quirks of these APIs.Ryan Smith - Monday, October 25, 2021 - link

Metal 2 is close enough in functionality and overhead to DX12 that I don't lose any sleep. But it is an API like any other, so devs need to be familiar with it to get the best performance from Apple's platform. Especially as Apple's GPU is a TBDR.Silma - Monday, October 25, 2021 - link

I don't understand how Intel, AMD and Qualcomm did not respond more urgently to the threat after the marketing of the M1.If they don't hurry, some people like me, who never considered switching to Apple, will entertain the idea.

willis936 - Monday, October 25, 2021 - link

It's 57 Bn transistors in a consumer SoC. How can companies who only sell SoCs compete with a company that sells their SoC at a loss?Ppietra - Monday, October 25, 2021 - link

"company that sells their SoC at a loss"????Apple is making profits when selling these machines so it cannot be selling at a loss.

What you could say is that Apple is not bound by the same manufacturing cost constrains as Intel or AMD because it doesn’t have to convince any other company to buy its chips.

phr3dly - Monday, October 25, 2021 - link

It would be really interesting to see the BOM for a MBP. It'll never happen of course, and direct comparisons to even an x86 MBP would be impossible.Certainly the vertical design gives Apple the opportunity to pocket what would otherwise be fat margins for Intel.

Ppietra - Monday, October 25, 2021 - link

Without a doubt Apple is taking advantage of not having to pay the for Intel (CPU) or AMD (GPU) margins.I am sure there will be some analyst trying to predict its cost – all iPhone BOM that you read do they same thing. Considering its size and some of the estimates for the previous M1 maybe somewhere close to 200 dollars for the M1 Max.

sirmo - Monday, October 25, 2021 - link

This chip is more expensive to manufacture than the 3090. It even has the wider memory bus. No way could you sell this as a component alone. Apple is clearly subsidizing this run to convince customers to stay for the transition.Ppietra - Monday, October 25, 2021 - link

How do you know that it is more expensive to manufacture than the 3090? And do you know how much the 3090 actually costs in order to come to such conclusion about "subsidizing"?? Wider memory bus has no relevance on how much the chip costs.Apple doesn’t sell computers at a loss, actually Apple almost certainly pays less for the chip than if it had to buy from Intel.

sirmo - Monday, October 25, 2021 - link

3090 is 28B transistors, this behemoth is 57B. As you go larger the yields get worse, so there is a bell curve to how high the costs ramp up. Also M1 Max is made on the most advanced 5nm node. Which is more expensive than Samsung's 8nm 3090 is made on.Like it would definitely cost more than a 3090, maybe even 3-4 more times more expensive.