A Closer Look at Latency and Scaling

As was explained in the Core 2 Duo launch review, Core 2 Duo has not physically added a memory controller on the processor. The memory controller is still part of the motherboard chipset that drives Core 2 Duo. Intel added features that perform intelligent look-aheads on the memory controller to behave like lower latency. As you saw on pages 2 and 3, ScienceMark 2.0 shows the "intelligent look-aheads" in Core 2 Duo to be extremely effective, with Core 2 Duo memory now exhibiting lower apparent latency than AM2. However, not all latency benchmarks show the same results. Everest from Lavalys shows latency improvements in the new CPU revisions, but it shows Latency more as we would expect in evaluating Conroe. For that reason, our detailed benchmarks for latency will use both Everest 1.51.195, which fully supports the Core 2 Duo processor, and ScienceMark 2.0.

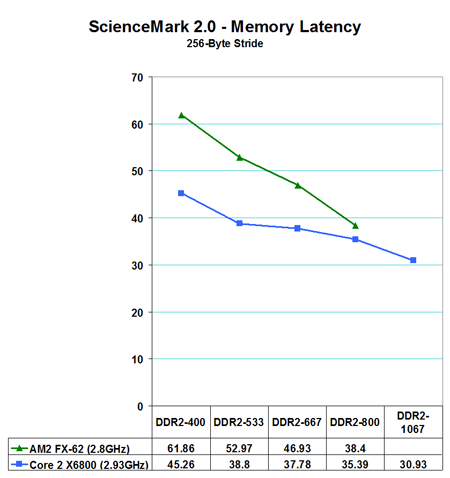

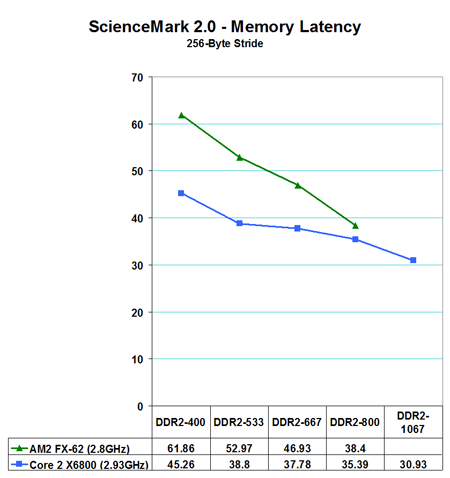

Latency, or how fast memory is accessed, is not a static measurement. It varies with memory speed and generally improves (goes down) as memory speed increases. To better understand what is happening with memory accesses we first looked at Sciencemark 2.0 Latency on both AM2 and Conroe.

ScienceMark shows Conroe Latency with a 45ns to 61ns lead at DDR2-400. Latency continues to decrease as memory speed increases with Core 2 Duo, reaching a value of about 30ns at DDR2-1067. The Trend line for AM2 is steeper than Core 2 Duo, increasing at a rapid rate until latency is virtually the same at DDR2-800.

It is very interesting that ScienceMark shows lower latency on Core 2 Duo than AM2, since we all know the on-chip AM2 controller has to be faster. We thought perhaps it was because all of the tested memory accesses could be contained in the shared 4MB cache of Core 2 Duo, but Alex Goodrich,one of the authors of ScienceMark, states that Version 2 is designed to test up to 16MB of memory, forseeing the day of larger caches. In addition he states the Core 2 duo prefetcher is clever enough to pick up all the patterns ScienceMark uses to "fool" hardware prefetchers. ScienceMark plans a revision with an algoritm that is harder to fool, but Alex commented that Conroe fooling their benchmark was "in itself a great indicator of performance".

Everest uses a different algorithm for measuring Latency, and it shows the on-chip AM2 DDR2 controller in the lead at all memory speeds, with Latency almost the same at the Core 2 Duo memory speed range of DDR2-400 to DDR2-533. However, the Everest trend lines are similar to those in ScienceMark, in that AM2 latency improves at a steeper rate than Core 2 Duo as memory speed increases.

The point to the Latency discussion is that, as expected, AMD has much more opportunity for performance improvement with memory speed increases in AM2. Intel will eventually reach the point, if the lines were extended, where they would have to move to an on-chip memory controller to further improve latency. This is not to take anything away from Intel's intelligent design on Core 2 Duo. They have found a solution that fixes a performance issue without requiring an on-chip controller - for now.

As was explained in the Core 2 Duo launch review, Core 2 Duo has not physically added a memory controller on the processor. The memory controller is still part of the motherboard chipset that drives Core 2 Duo. Intel added features that perform intelligent look-aheads on the memory controller to behave like lower latency. As you saw on pages 2 and 3, ScienceMark 2.0 shows the "intelligent look-aheads" in Core 2 Duo to be extremely effective, with Core 2 Duo memory now exhibiting lower apparent latency than AM2. However, not all latency benchmarks show the same results. Everest from Lavalys shows latency improvements in the new CPU revisions, but it shows Latency more as we would expect in evaluating Conroe. For that reason, our detailed benchmarks for latency will use both Everest 1.51.195, which fully supports the Core 2 Duo processor, and ScienceMark 2.0.

Latency, or how fast memory is accessed, is not a static measurement. It varies with memory speed and generally improves (goes down) as memory speed increases. To better understand what is happening with memory accesses we first looked at Sciencemark 2.0 Latency on both AM2 and Conroe.

ScienceMark shows Conroe Latency with a 45ns to 61ns lead at DDR2-400. Latency continues to decrease as memory speed increases with Core 2 Duo, reaching a value of about 30ns at DDR2-1067. The Trend line for AM2 is steeper than Core 2 Duo, increasing at a rapid rate until latency is virtually the same at DDR2-800.

It is very interesting that ScienceMark shows lower latency on Core 2 Duo than AM2, since we all know the on-chip AM2 controller has to be faster. We thought perhaps it was because all of the tested memory accesses could be contained in the shared 4MB cache of Core 2 Duo, but Alex Goodrich,one of the authors of ScienceMark, states that Version 2 is designed to test up to 16MB of memory, forseeing the day of larger caches. In addition he states the Core 2 duo prefetcher is clever enough to pick up all the patterns ScienceMark uses to "fool" hardware prefetchers. ScienceMark plans a revision with an algoritm that is harder to fool, but Alex commented that Conroe fooling their benchmark was "in itself a great indicator of performance".

Everest uses a different algorithm for measuring Latency, and it shows the on-chip AM2 DDR2 controller in the lead at all memory speeds, with Latency almost the same at the Core 2 Duo memory speed range of DDR2-400 to DDR2-533. However, the Everest trend lines are similar to those in ScienceMark, in that AM2 latency improves at a steeper rate than Core 2 Duo as memory speed increases.

The point to the Latency discussion is that, as expected, AMD has much more opportunity for performance improvement with memory speed increases in AM2. Intel will eventually reach the point, if the lines were extended, where they would have to move to an on-chip memory controller to further improve latency. This is not to take anything away from Intel's intelligent design on Core 2 Duo. They have found a solution that fixes a performance issue without requiring an on-chip controller - for now.

118 Comments

View All Comments

Zebo - Tuesday, July 25, 2006 - link

Nice one Wes and it makes sense no matter what to have memory testing done on the top dog platform, Conroe.Mclendo06 - Tuesday, July 25, 2006 - link

Is there any reason that either company, Intel or AMD, couldn't design a future processor both with an intelligent pre-fetching algorithm such as is seen in the Core 2 Duo and an on-die memory controller like on the AM2 processors? Seems like the apparent memory latencies could be dropped very significantly by combining these features.Calin - Tuesday, July 25, 2006 - link

We are hoping in the next big update to AMD processor (the K8L) to have some kind of intelligent prefetching (it is entirely possible, but it costs a number of transistors). Possibly that "intelligent prefetching" means reordering loads from memory, and this happens before the memory controllerIngas - Tuesday, July 25, 2006 - link

How can Core 2 Duo do prefetch before memory controller?

I miss some point, do I?

Calin - Wednesday, July 26, 2006 - link

I wasn't clear enough. The memory controller gets requests for memory, and returns that memory. Nothing more, nothing less.All the logic for preordering is housed in the proper microprocessor, and not in the memory controller - as such, it has no relation with the integrated/discrete implementation of the memory controller.

vailr - Tuesday, July 25, 2006 - link

Has anyone run: a Core2 Duo CPU comparison of DDR vs. DDR2, running on the ASrock 775Dual-VSTA? To determine how much slowdown would occur, by using the older DDR memory?Ingas - Tuesday, July 25, 2006 - link

Interesting point!Maybe Core intelligent look-ahead so intelligent, that it even performs equaly on DDR!

Hm.

Very interesting!

Gary Key - Tuesday, July 25, 2006 - link

We will show this in our review. ASRock just released bios 1.4 that addressed a few issues we noticed in our preview of the board.photoguy99 - Tuesday, July 25, 2006 - link

...that AMD is thoroughly owned.It's amazing the arguments have still persisted up until now about excuses for Core2 doing so well.

It was mentioned that AMD survived before at the lower end of the market - but remember how much trouble they had? There were losing money all the time back then. Now they have taken *all* of their 2.5B cash reserve and spent it on ATI. Nice.

It hurt AMD's credibility even more when Dirk Diggler recently said 4x4 was going to be an answer to Core2. Right. After 30 years of dual socket systems being a niche they are finally going to take off and save you - good luck with that.

duploxxx - Tuesday, July 25, 2006 - link

because you have no idea what is going behind the scene and only looking at performance of a desktop cpu and think this is the real world.almost no review site is proud enough to get up against the hyping marketing machine from intel. well then believe the marketing hype and own a cpu that has a crapy design when it comes to real multithread and 64bit. way to go to the future knowing vista is comming your way.

multicore/multisocket is the future, even intel knows it.

amd is in a much stronger position know and by the end of this year the make procs with a price tag 50% lower than intel intel can only counter this by going to 45nm end of 2007. knowing the cost of all the intel crew, fabs and size of the processors.