AMD Previews EPYC ‘Rome’ Processor: Up to 64 Zen 2 Cores

by Anton Shilov on November 6, 2018 2:27 PM EST

AMD on Tuesday formally announced its next-generation EPYC processor code-named Rome. The new server CPU will feature up to 64 cores featuring the Zen 2 microarchitecture, thus providing at least two times higher performance per socket than existing EPYC chips.

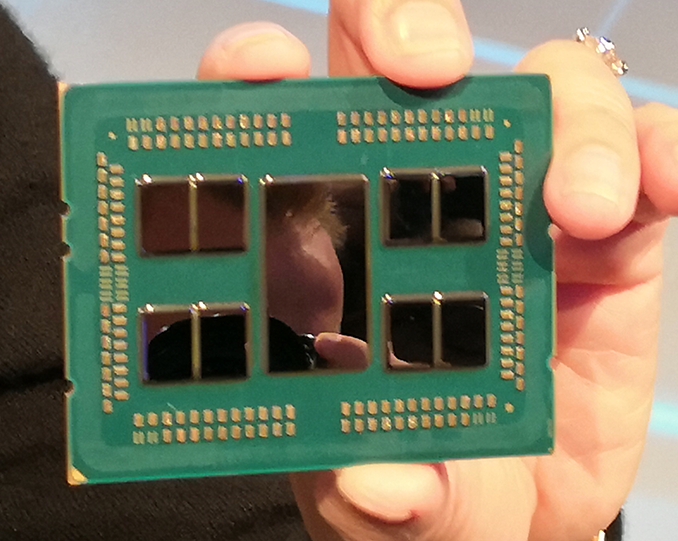

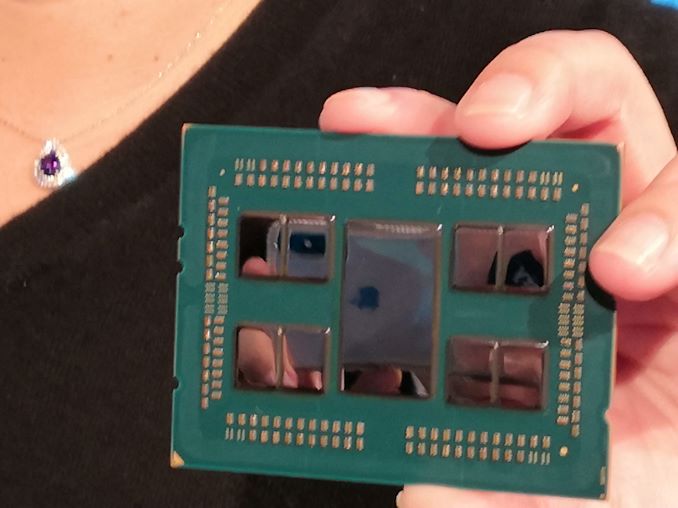

As discussed in a separate story covering AMD’s new ‘chiplet’ design approach, AMD EPYC ‘Rome’ processor will carry multiple CPU chiplets manufactured using TSMC’s 7 nm fabrication process as well as an I/O die produced at a 14 nm node. As it appears, high-performance ‘Rome’ processors will use eight CPU chiplets offering 64 x86 cores in total, as well as an eight-channel DDR4 memory controller supporting up to 4 TB of DRAM per socket. Besides, the new processor supports 128 PCIe 4.0 lanes to connect next-generation accelerators, such as the Radeon Instinct MI60 based on the Vega 7nm GPU.

Considering the fact that Zen 2 microarchitecture is expected to generally increase performance of CPU cores (especially when it comes to floating point performance, which AMD expects to double), the Rome processors will boost performance of servers quite dramatically when compared to existing machines. In particular, AMD expects performance per socket to double as a result of higher core count, and predicts that floating point performance per socket will quadruple because of arhitectural IPC improvements and increase of the core count.

One important peculiarity of AMD’s EPYC ‘Rome’ processor is that it is socket compatible with existing EPYC ‘Naples’ platform and will be forward compatible with AMD’s future ‘Milan’ platforms featuring CPUs powered by the Zen 3 microarchitecture. This will greatly simplify development of AMD-based servers and will enable server makers to reuse their existing designs for future machines, which is important for AMD that needs to capture market from Intel. To do that, it has to simplify job of server builders by making its platforms simple.

AMD is currently sampling its EPYC ‘Rome’ processor with server makers and customers. The company plans to launch ‘Rome’ products sometimes in 2019, but it does not disclose its launch schedule just now.

This is a breaking news. We are updating the news story with more details.

67 Comments

View All Comments

ChaosFenix - Tuesday, November 6, 2018 - link

So is it just me or does that look like a GPU in the middle there? It looks to be too big to be HBM2 and you can clearly see the placement of the 8*8 CCX's on the side. Is that a massive GPU in the middle of that thing?kalgriffen - Tuesday, November 6, 2018 - link

It's an I/O chip for the processor dies.SaturnusDK - Tuesday, November 6, 2018 - link

It even says so in the 2 paragraph article. Short attention span or what?ChaosFenix - Tuesday, November 6, 2018 - link

Oh I didn't realize that die was dedicated to IO. Interesting to break it off like that then.phoenix_rizzen - Tuesday, November 6, 2018 - link

Read the linked "chiplet design approach" article. :)That's the I/O hub, which comprises the memory controllers, the Infinity Fabric, and so on.

The CPU chiplets are fabbed on a 7nm process; the I/O hub is fabbed on a 14nm process.

Arbie - Tuesday, November 6, 2018 - link

Can't you tell from the photo? The forehead shows it's an AI module.SaturnusDK - Tuesday, November 6, 2018 - link

Intel gotta turn up the AC now as the sweating under the brow across the Bayshore Freeway is going to be relentless in the coming years.philehidiot - Saturday, November 10, 2018 - link

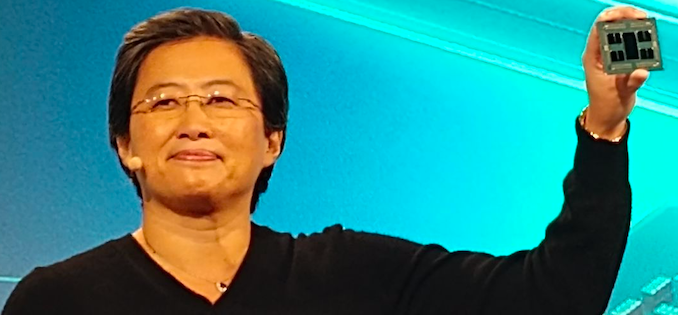

So she's got AMD properly back into the game, got an AMD GPU into my system for the first time in ages and, as the proverbial cherry, she's caning Intel's electricity bill with increased AC requirements.That is one formidable woman.

outsideloop - Tuesday, November 6, 2018 - link

So, is Ryzen 2 going to have one or two of those little 8 core chiplets? Plus the I/O chip? or maybe a smaller I/O chip than that? :)SaturnusDK - Tuesday, November 6, 2018 - link

Ryzen 3000 series doesn't need 8 DDR4 lanes or 8 dual Infinity Fabric controllers, so yes, the I/O chip for that will be about 1/4 the size.