GIGABYTE Teases PCIe 4.0 M.2 SSD in Press Release: 5 GB/s

by Anton Shilov on May 24, 2019 9:10 PM EST

A press release sent out by GIGABYTE on Friday said that the company would demonstrate one of the industry’s first SSDs featuring a PCIe 4.0 interface at Computex next week. The company says that its drive will offer maximum sequential read/write speeds of up to 5 GB/s. when used with AMD’s upcoming Ryzen 3000-series platform supporting PCIe 4.0.

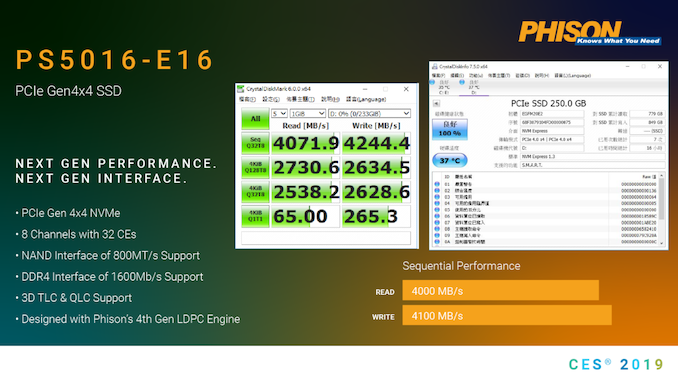

GIGABYTE is a rather new player on the SSD market and at present the company only offers drives based on controllers from Phison. Therefore, it is more than likely that GIGABYTE will showcase a PCIe 4.0 x4 SSD based on Phison’s PS5016-E16 controller that the chip developer demonstrated earlier this year at CES 2019. Keep in mind though that GIGABYTE has not officially confirmed use of the Phison controller.

The Phison PS5016-E16 processor has 8 NAND channels with 32 CE targets that supports interface speeds of up to 800 MT/s. Featuring Phison’s 4th Gen LDPC ECC engine, the controller can support both 3D TLC and 3D QLC NAND flash memory. To ensure high performance, it can also support a DDR4-1600 DRAM buffer.

One interesting thing to note about the SSD that GIGABYTE plans to demonstrate is that it was published as that it will offer up to 5 GB/s read/write speeds ‘in low temperatures’, which suggests that this drive will require a sophisticated cooling to show all of its advantages. It is also noteworthy that 5 GB/s speeds will likely be hit by high-capacity drives only given 8 NAND channels at 800 MT/s featured by the controller.

It is noteworthy that back in January a prototype SSD powered by the PS5016-E16 could only offer 4/4.2 GB/s read/write speeds. Given GIGABYTE’s performance figures, it is evident that Phison has managed to significantly boost performance of SSDs based on its controller in less than half of a year.

Computex 2019 trade show will take place in Taipei, Taiwan, from May 28 to June 1, 2019.

Related Reading:

- The GIGABYTE Aorus RGB M.2 SSD Review: Nothing Is Too Small For RGB LEDs

- Patriot Launches Viper VPN100 SSDs: Up to 2TB, Massive Heatsink

- OSS Unveils 5-Way PCIe 4.0 Backplane, Demonstrates PCIe 4.0 HPC Platform

- Microsemi Announces PCIe 4.0 Switches And NVMe SSD Controller

Source: GIGABYTE

| Want to keep up to date with all of our Computex 2019 Coverage? | ||||||

Laptops |

Hardware |

Chips |

||||

| Follow AnandTech's breaking news here! | ||||||

42 Comments

View All Comments

Ej24 - Friday, May 24, 2019 - link

Honestly what I'd prefer is to see lots of devices using half the number of lanes while achieving the same bandwidth as today. You'd immediately get twice as many lanes to work with. Pcie 4.0 x8 would be the same as x16 on pcie 3.0. You'd now have another 8 lanes of pcie 4.0 to play with. You'd only need 2 lanes to get nvme speeds that require 4 lanes today. Only super fast nvme drives are pushing the limits on pcie 3.0 x4 anyway. The i/o capabilities would be nuts for a mainstream desktop if they could implement it as such. I realize though that all said peripherals would need to be pcie 4.0 or they won't get that double bandwidth per lane. That's a while away.nevcairiel - Saturday, May 25, 2019 - link

Limiting a GPU to 8x is easy - just plug in a second device, and the mainboard will split it. Some even support 8/4/4 splits (at least Intel boards, don't remember seeing an AM4 with that, but thats not a AM4 limitation, so board makers could make it), so you can put a duo NVMe SSD card in one slot, and whatever fancies you in another.All that needs is PCIe4 everything, as you say.

Chaitanya - Sunday, May 26, 2019 - link

X470 based Asus Crosshair is the only Am4 mainboard that allows for 8/4/4 pci-e splitting for GPU and SSD Raid.PixyMisa - Saturday, May 25, 2019 - link

AMD's X570 chipset effectively gives you that. It has 4 PCIe 4.0 lanes to the CPU, and 16 PCIe 4.0 lanes for devices. You can't run them all at full speed, but you can run two SSDs at PCIe 3.0 x 4 speed.cb88 - Saturday, August 10, 2019 - link

The links to the devices hanging off of the X570 chipset are 4.0 links though, so you could put a 4.0 SSD on it and get max bandwidth out of it if you weren't using bandwidth on any other devices... I imagine DMA between devices on the x570 chipset also doesnt' suffer since it shouldn't have to go through the slow 4x link thought that doesn't have much application outside of perhaps RAID and server applicaitons maybe?Alexvrb - Saturday, May 25, 2019 - link

That shouldn't be done at a device level. If the device can utilize 4 PCIe 4.0 lanes, it will work fine in a number of configurations including two lanes and PCIe 3.0. Why gimp the actual device itself? If you want a device that's slower, there will always be low-end options, but lane reduction should be handled at the board level. Which as the others have already said, board manufacturers already configure splits for users with more devices. That's a better way of handling it.Oh and what's "nuts" and "super fast" today is mainstream in a year or so. :D

Santoval - Sunday, May 26, 2019 - link

What makes you think that the lower cost M.2 SSDs will not based on two PCIe 4.0 lanes, just like they are based today on two PCIe 3.0 lanes? The transition to PCIe 4.0 allows both to double the bandwidth of the low cost M.2 SSDs and to double the bandwidth of the higher cost M.2 SSDs (or rather the bandwidth of the SSDs *can* double, since for the first 3 years at least they will be nowhere close to saturating the bandwidth of their x2 or x4 PCIe link).In plenty of cases half the lanes will be used for the same bandwidth, not just with M.2 SSDs but with x8 and x16 PCIe slots and devices. The transition to PCIe 4.0 (and eventually to PCIe 5.0) allows that flexibility.

sorten - Friday, May 24, 2019 - link

Can't wait until Sunday when I can read about the hardware that going in my next PC build.Freeb!rd - Saturday, May 25, 2019 - link

D!tto.Slash3 - Friday, May 24, 2019 - link

Link to press release: https://www.gigabyte.com/Press/News/1690